- 545.38 KB

- 6页

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

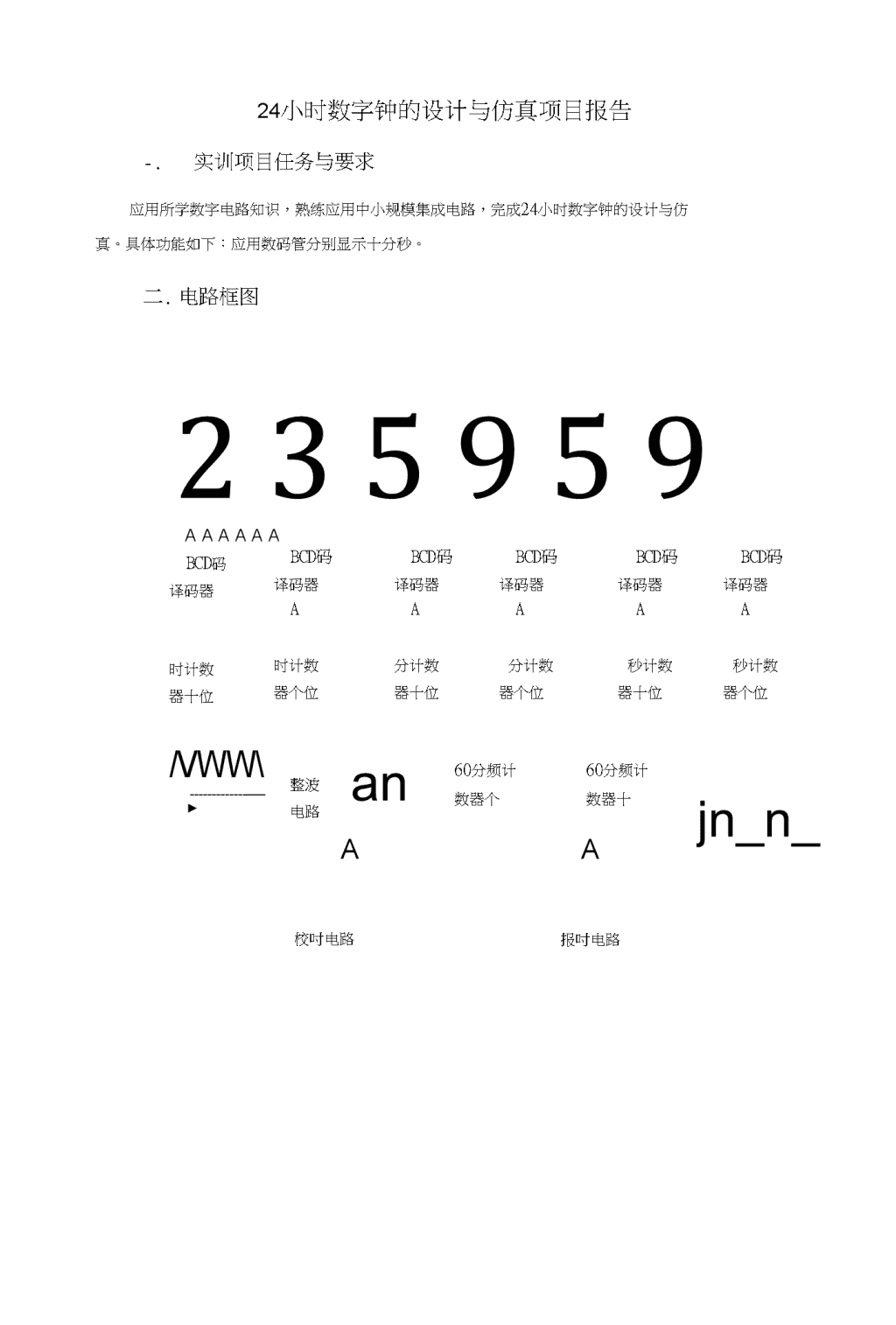

'24小时数字钟的设计与仿真项目报告-.实训项目任务与要求应用所学数字电路知识,熟练应用中小规模集成电路,完成24小时数字钟的设计与仿真。具体功能如下:应用数码管分别显示十分秒。二.电路框图235959AAAAAABCD码译码器时计数器十位BCD码译码器A时计数器个位BCD码译码器A分计数器十位BCD码译码器A分计数器个位BCD码译码器A秒计数器十位BCD码译码器A秒计数器个位/VWW►整波电路an60分频计60分频计数器个数器十jn_n_AA报吋电路校吋电路

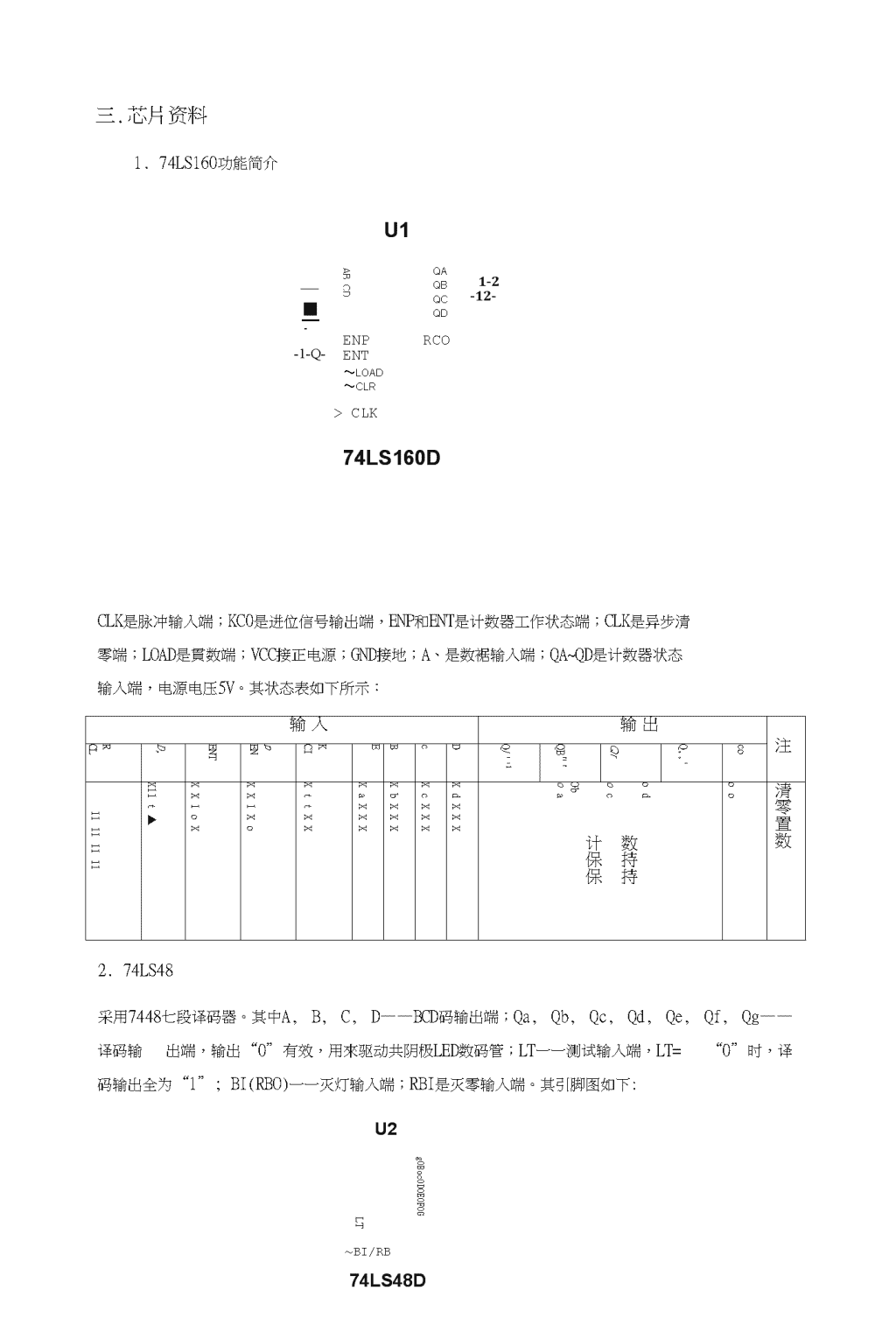

二.芯片资料1.74LS160功能简介U1■I-1-Q-QAQBQCQDENPRCOENTABCD1-2-12-〜LOAD〜CLR>CLK74LS160DCLK是脉冲输入端;KC0是进位信号输出端,ENP和ENT是计数器工作状态端;CLK是异步清零端;LOAD是貫数端;VCC接正电源;GND接地;A、是数裾输入端;QA~QD是计数器状态输入端,电源电压5V。其状态表如下所示:入输出输注RCLD,ENTpENKCIEBcDQ/""1qb""QrQ,,"co11111111X11t▲XX1oXXX1XoXttXXXaXXXXbXXXXcXXXXdXXXod数持持oc计保保Oboaoo清零置数2.74LS48采用7448七段译码器。其中A,B,C,D——BCD码输出端;Qa,Qb,Qc,Qd,Qe,Qf,Qg——译码输出端,输出“0”有效,用來驱动共阴极LED数码管;LT一一测试输入端,LT=“0”时,译码输出全为“1”;BI(RBO)一一灭灯输入端;RBI是灭零输入端。其引脚图如下:U2LT〜BI/RBOgOBocODOEOFOG74LS48D

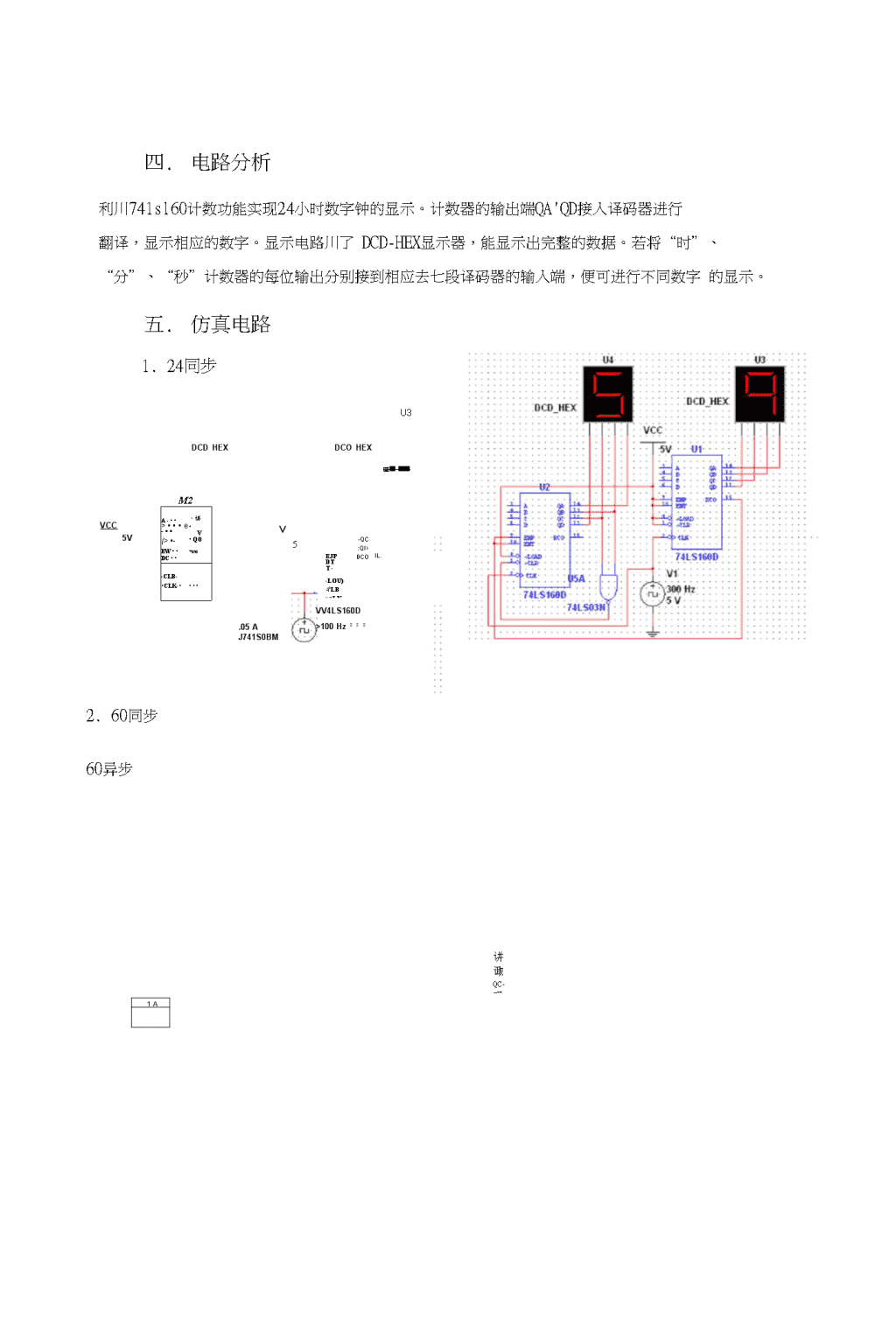

二.电路分析利川741sl60计数功能实现24小时数字钟的显示。计数器的输出端QA"QD接入译码器进行翻译,显示相应的数字。显示电路川了DCD-HEX显示器,能显示出完整的数据。若将“时”、“分”、“秒”计数器的每位输出分别接到相应去七段译码器的输入端,便可进行不同数字的显示。三.仿真电路VCC5V1.24同步DCDHEXM2A-•••讲>•••e-•••Vj>•-•QOEW•••woDC••-CLB-•CLK-••••v<5V.05AJ741S0BMVV4LS160D>100Hz:::DCOHEXEJPDTT--LOU)彳LB»BCOU3匾■■■IL.2.60同步60异步讲诹QC-吸:1A

A•••B•••■队•Q&c••-D••••QC.•QDEHP..EOT..•RCO々LOAD••••々CLR.••••>CLK•-•豢鬱••••I?EC

100同步IlfDCDHEXvceU1A••••VC€«■GKD••••-JZ-ULU2JL5^-IE.A•••VCor••••••RCO々CLB•••->CDC-GKD••••-JJL士-IE.-U-iioDCDHEXr=«L^ivviy100异步inVfC•—5V十0:•似74LS160NDCDJiEXB••-D•••OT••an••-L6AD-74LS05D总图DCD_HBX

'

您可能关注的文档

- 台山养和肾析血液透析有限公司建设项目报告表

- 辽宁经济职业技术学院管理系毕业项目报告(陈秀静)

- 弧焊电源项目报告

- 1、青岛耐固工业自动化有限公司车辆零部件生产项目报告表-审

- 中原常州嘉宏集团—戚墅堰项目报告

- 肿瘤中心项目报告__[全套]设备购置

- 黔西县烟地机械化耕作项目报告

- 上海聚浪-启东五洲项目报告

- 世纪瑞博世茂集团北京大厂项目报告

- 安乡三岔河镇中心卫生院建设项目报告表

- 《软件项目报告》word版

- 容器化育苗基地项目报告

- 刺梨项目报告内容

- 新闻管理系统项目报告

- 甘肃天水传染病医院项目报告书

- 山西省通信公司晋城市分公司营销咨询项目报告第二部分营销战略

- 贵阳中华北路综合体项目报告(126页)

- network文件存储与恢复项目报告