- 152.50 KB

- 17页

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

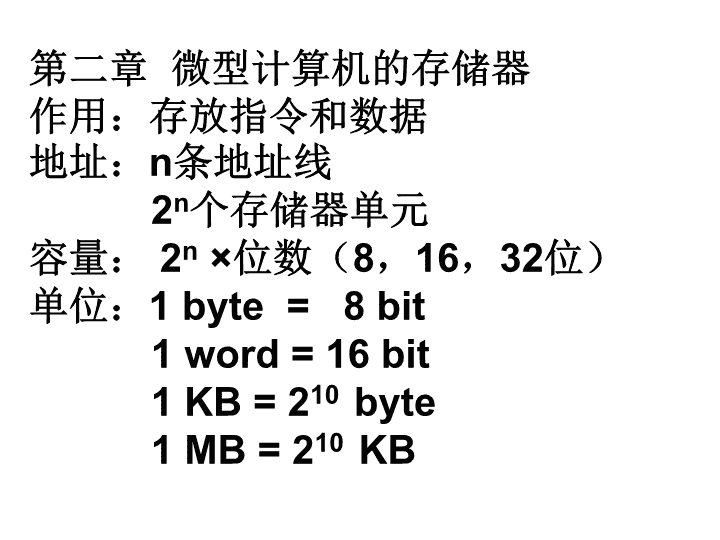

第二章微型计算机的存储器

作用:存放指令和数据

地址:n条地址线

2n个存储器单元

容量:2n×位数(8,16,32位)

单位:1byte=8bit

1word=16bit

1KB=210byte1MB=210KB

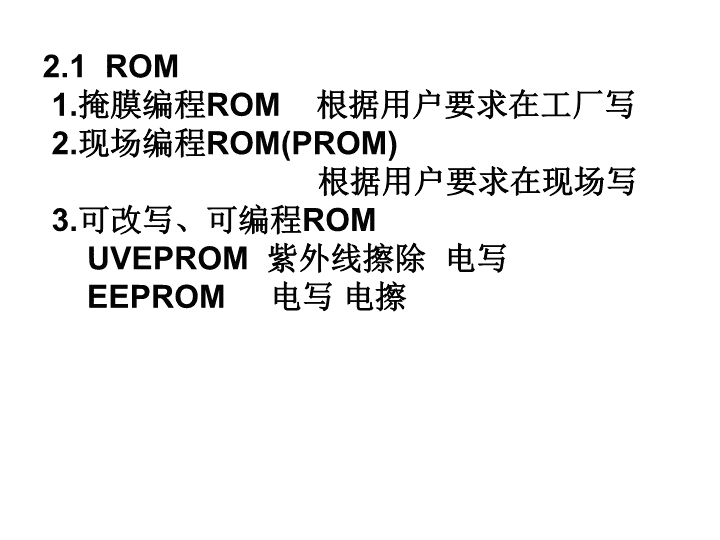

2.1ROM1.掩膜编程ROM根据用户要求在工厂写2.现场编程ROM(PROM)根据用户要求在现场写3.可改写、可编程ROMUVEPROM紫外线擦除电写EEPROM电写电擦

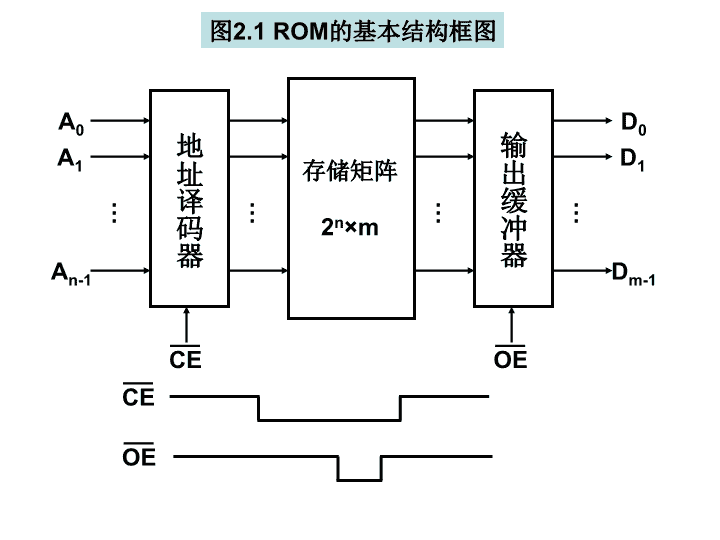

地址译码器输出缓冲器存储矩阵2n×m…………A0A1An-1D0D1Dm-1图2.1ROM的基本结构框图CEOECEOE

VccCE/PGMA10OEA72716EPROMA6A5A4A3A2A1A0O0O1O2GND1357911242220181614O7O6O5O4O3VppA8A9引脚状态方式CE/PGMOEVpp(V)Vcc(V)输出值读出低低+5+5数据输出维持高无关+5+5高阻抗编程脉冲高+25+5数据输入程序检验低低+25+5数据输出编程禁止低高+25+5高阻抗图2.52716的引脚排列表2.12716的工作方式

2.2RAM1.静态RAM有电保持,内部复杂,集成度低2.动态RAM有电刷新,外部刷新,集成度高3.Flash存储器

图2.62128的引脚排列表2.22128的工作方式VccCEA10OEA72128SRAMA6A5A4A3A2A1A0I0/O0GND1357911242220181614I7/O7WEA8A9I1/O1I2/O2I6/O6I5/O5I4/O4I3/O3数据输入低低任意写入数据输出低高低读出高阻抗低高高输出禁止高阻抗高任意任意未选中DCEWEOE引脚状态方式

2.3存储器的组成与扩展2.3.1芯片的选择1.类型选择ROM:掩膜ROMPROMUVEPROMEEPROMRAM:静态RAM动态RAMFlash2.容量选择27162Kbyte2751264Kbyte3.存储器的存取时间与CPU速度的匹配CPU速度:送出地址有效到送出读写信号存取时间:读取时间(较长)、写入时间读取时间:CPU地址有效到存储器数据稳定

地址有效读完成CPU信号存储器最大读取时间TrFs=20MTs=50nsTr=200ns存储器1Tr=100ns适合存储器2Tr=210ns不适合

2.3存储器的组成与扩展2.3.2存储器芯片组的连接AddressBusDataBusControlBusCPU存储器

1。位数的扩展8位扩展成为16位AddressBusDataBus(low8)ControlBusCPU低8位存储器高8位存储器DataBus(up8)地址线、控制线并接,数据线分开接

2.存储器存储单元的扩展用4片2K*8位扩展成为8K*8位存储器芯片组(1)每片有地址线11根(并接到CPU),数据线8根(并接到CPU);(2)片选线1根。在4片的4根片选线分别接到CPU,任何时间只能有一根片选线出现有效电平(高/低,1/0)。(3)线选法译码法全译码,部分译码使用译码器

(3)线选法译码法全译码,部分译码使用译码器A12/4译码器A00123A1A03210001110011101101011110111

芯片A15A14A13A12A11A10…A0地址范围#1000010…00800~0FFF000011…1#2000100…01000~17FF000101…1#3001000…02000~27FF001001…1#4010000…04000~47FF010001…1A0~A108位DB图2.13用线选法扩展存储器单元数#1#2#3#4A11A12A13A14高有效

A0~A108位DB图2.13用线选法扩展存储器单元数芯片A15A14A13A12A11A10…A0地址范围#1011100…07000011101…1~77FF#2011010…06800011011…1~6FFF#3010110…05800010111…1~5FFF#4001110…03800001111…1~3FFF#1#2#3#4A11A12A13A14低有效

A0~A158位DB图2.14全译码法构成8k×8存储器芯片A15A14A13A12A11A10…A0地址范围#1000000…00000~07FF000001…1#2000010…00800~0FFF000011…1#3000100…01000~17FF000101…1#4000110…01800~1FFF000111…1CE#41800~1FFFCE#31000~17FFCE#20800~0FFFCE#10000~07FFQ0Q1Q2Q3A0~A10A11~A155/32译码器

A0~A128位DB图2.15采用部分译码的连接方案A15A14A13芯片A12A11A10…A0基本地址范围000#1000…00000~07FF001001…1010#2010…00800~0FFF011011…1100#3100…01000~17FF101101…1110#4110…01800~1FFF111111…1CE#41800~1FFFCE#31000~17FFCE#20800~0FFFCE#10000~07FFQ0Q1Q2Q3A11~A122/4译码器

译码方式比较线选法部分地址译码全地址译码地址连续NYY多占地址YYN加译码器NYY